/ README.md

README.md

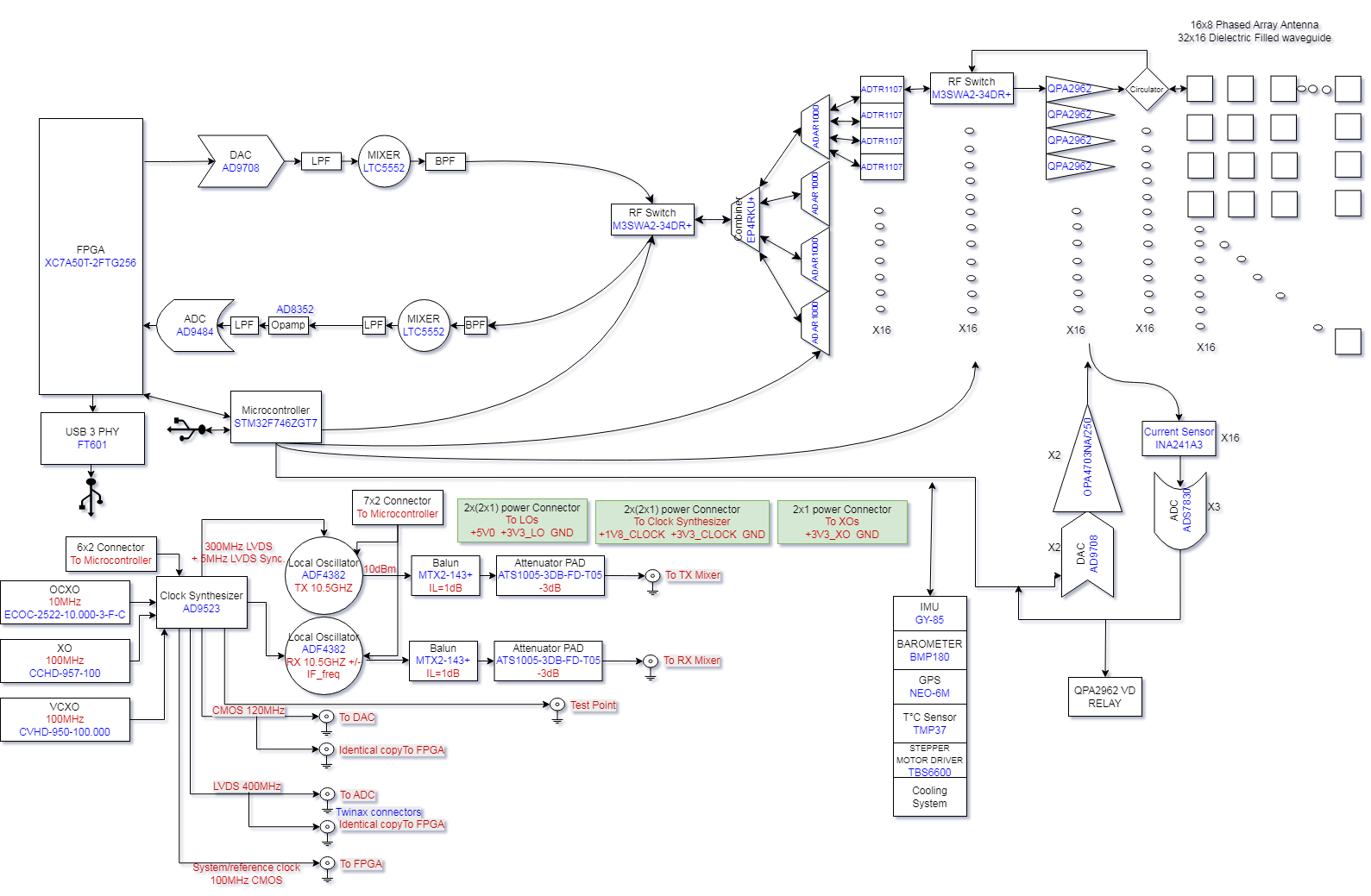

1 # AERIS-10: Open Source Pulse Linear Frequency Modulated Phased Array Radar 2 3 [](https://ohwr.org/cern_ohl_p_v2.txt) 4 [](https://opensource.org/licenses/MIT) 5 [](https://github.com/NawfalMotii79/PLFM_RADAR) 6 [](https://github.com/NawfalMotii79/PLFM_RADAR) 7 [](https://github.com/NawfalMotii79/PLFM_RADAR/pulls) 8 9  10 11 AERIS-10 is an open-source, low-cost 10.5 GHz phased array radar system featuring Pulse Linear Frequency Modulated (LFM) modulation. Available in two versions (3km and 20km range), it's designed for researchers, drone developers, and serious SDR enthusiasts who want to explore and experiment with phased array radar technology. 12 13  14 15 ## 📡 Overview 16 17 The AERIS-10 project aims to democratize radar technology by providing a fully open-source, modular, and hackable radar system. Whether you're a university researcher, a drone startup, or an advanced maker, AERIS-10 offers a platform for experimenting with beamforming, pulse compression, Doppler processing, and target tracking. 18 19 ## 🔬 Key Features 20 21 - **Open Source Hardware & Software** - Complete schematics, PCB layouts, firmware, and software available 22 - **Dual Version Availability**: 23 - **AERIS-10N (Nexus)**: 3km range with 8x16 patch antenna array 24 - **AERIS-10E (Extended)**: 20km range with 32x16 dielectric-filled slotted waveguide array 25 - **Full Electronic Beam Steering** - ±45° electronic steering in elevation and azimuth 26 - **Advanced Signal Processing** - On-board FPGA handles pulse compression, Doppler FFT, MTI, and CFAR 27 - **Python GUI** - User-friendly interface with map integration 28 - **GPS/IMU Integration** - Real-time position and attitude correction 29 - **Modular Design** - Separate power management, frequency synthesis, and RF boards 30 31 ## 🏗️ System Architecture 32 33  34 35 ### Hardware Components 36 37 The AERIS-10 main sub-systems are: 38 39 - **Power Management Board** - Supplies all necessary voltage levels to the electronics components with proper filtering and sequencing (sequencing ensured by the microcontroller) 40 41 - **Frequency Synthesizer Board** - Uses a high-performance Low Jitter Clock Generator (AD9523-1) that supplies phase-aligned clock references for: 42 - RX and TX Frequency Synthesizers (ADF4382) 43 - DAC 44 - ADC 45 - FPGA 46 47 - **Main Board** containing: 48 - **DAC** - Generates the RADAR Chirps 49 - **2x Microwave Mixers (LT5552)** - For up-conversion and IF-down-conversion 50 - **4x 4-Channel Phase Shifters (ADAR1000)** - For RX and TX chain beamforming 51 - **16x Front End Chips (ADTR1107)** - Used for both Low Noise Amplifying (RX) and Power Amplifying (TX) stages 52 - **XC7A50T FPGA** - Handles RADAR Signal Processing on the upstream FTG256 board: 53 - PLFM Chirps generation via the DAC 54 - Raw ADC data read 55 - Automatic Gain Control (AGC) 56 - I/Q Baseband Down-Conversion 57 - Decimation 58 - Filtering 59 - Forward FFT 60 - Pulse Compression 61 - Doppler, MTI and CFAR processing 62 - USB Interface 63 - **STM32F746xx Microcontroller** - Used for: 64 - Power-up and power-down sequencing (see Power Management Excel File) 65 - FPGA communication 66 - Setup and Interface with: 67 - Clock Generator (AD9523-1) 68 - 2x Frequency Synthesizers (ADF4382) 69 - 4x 4-Channel Phase Shifters (ADAR1000) for RADAR pulse sequencing 70 - 2x ADS7830 ADCs (on Power Amplifier Boards) for Idq measurement 71 - 2x DAC5578 (on Power Amplifier Boards) for Vg control 72 - GPS module for GUI map centering 73 - GY-85 IMU for pitch/roll correction of target coordinates 74 - BMP180 Barometer 75 - Stepper Motor 76 - 8x ADS7830 Temperature Sensors for cooling fan control 77 - RF switches 78 79 - **16x Power Amplifier Boards** - Used only for AERIS-10E version, featuring 10Watt QPA2962 GaN amplifier for extended range 80 81 - **Antenna Arrays**: 82 - **AERIS-10N (Nexus)** - 8x16 patch antenna array 83 - **AERIS-10X (Extended)** - 32x16 dielectric-filled slotted waveguide antenna array 84 85 - **Miscellaneous Components**: 86 - Slip-Ring 87 - Stepper Motor and drivers 88 - Cooling Fans 89 - Enclosure 90 91 ### Processing Pipeline 92 93 1. **Waveform Generation** - DAC creates LFM chirps 94 2. **Up/Down Conversion** - LT5552 mixers handle frequency translation 95 3. **Beam Steering** - ADAR1000 phase shifters control 16 elements 96 4. **Signal Processing (FPGA)**: 97 - Raw ADC data capture 98 - I/Q baseband down-conversion 99 - Decimation & filtering (CIC/FIR) 100 - Pulse compression 101 - Doppler FFT processing 102 - MTI & CFAR detection 103 5. **System Management (STM32)**: 104 - Power sequencing 105 - Peripheral configuration 106 - GPS/IMU integration 107 - Stepper motor control 108 6. **Visualization (Python GUI)**: 109 - Real-time target plotting 110 - Map integration 111 - Radar control interface 112 113  114 115 ## 📊 Technical Specifications 116 117 | Parameter | AERIS-10N (Nexus) | AERIS-10X (Extended) | 118 |-----------|-------------------|----------------------| 119 | **Frequency** | 10.5 GHz | 10.5 GHz | 120 | **Max Range** | 3 km | 20 km | 121 | **Antenna** | 8x16 Patch Array | 32x16 Slotted Waveguide | 122 | **Beam Steering** | Electronic (±45°) | Electronic (±45°) | 123 | **Mechanical Scan** | 360° (stepper motor) | 360° (stepper motor) | 124 | **Output Power** | ~1W×16 | 10W×16 (GaN amplifier) | 125 | **Processing** | FPGA + STM32 | FPGA + STM32 | 126 127 ## 🚀 Getting Started 128 129 ### 🧹 Repository File Placement Policy 130 131 To keep the repository root clean and make artifacts easy to find, place generated files in the following locations: 132 133 - **Published reports (tracked, GitHub Pages):** `docs/` 134 - Example: `docs/AERIS_Simulation_Report_v2.pdf` 135 - **Simulation-generated outputs (local, gitignored):** `5_Simulations/generated/` 136 - Plots, scenario outputs, temporary analysis directories 137 - **FPGA/Vivado generated artifacts (local, gitignored):** `9_Firmware/9_2_FPGA/reports/` 138 - VCD/VVP dumps, temporary CSVs, local report snapshots 139 - **Reusable FPGA automation scripts (tracked):** `9_Firmware/9_2_FPGA/scripts/` 140 - TCL flows, helper scripts used by build/bring-up 141 142 **Do not leave generated artifacts in the repository root.** 143 144 ### Prerequisites 145 146 - Basic understanding of radar principles 147 - Experience with PCB assembly (for hardware build) 148 - Python 3.8+ for the GUI software 149 - FPGA development tools (Vivado) for signal processing modifications 150 151 ### Hardware Assembly 152 153 1. **Order PCBs**: Production outputs are under `/4_Schematics and Boards Layout/4_7_Production Files` 154 2. **Source Components**: BOM/CPL files are co-located under `/4_Schematics and Boards Layout/4_7_Production Files` 155 3. **Assembly**: Use the schematics in `/4_Schematics and Boards Layout/4_6_Schematics` together with the production outputs above; a standalone assembly guide is not currently tracked 156 4. **Antenna**: Choose appropriate array files for your target variant 157 5. **Enclosure**: Mechanical drawings currently live in `/8_Utils/Mechanical_Drawings` 158 159 ## 📜 License 160 161 This project is open-source but uses **different licenses for hardware and software** to ensure proper legal coverage. 162 163 ### Hardware Documentation 164 The hardware design files—including: 165 - Schematics and PCB layouts (in `/4_Schematics and Boards Layout`) 166 - Bill of Materials (BOM) files 167 - Gerber files and manufacturing outputs 168 - Mechanical drawings and enclosure designs 169 170 are licensed under the **CERN Open Hardware Licence Version 2 – Permissive (CERN-OHL-P)** . 171 172 This is a hardware-specific license that: 173 - ✅ Clearly defines "Hardware," "Documentation," and "Products" 174 - ✅ Includes explicit patent protection for contributors and users 175 - ✅ Provides stronger liability limitations (important for high-power RF) 176 - ✅ Aligns with professional open-hardware standards (CERN, OSHWA) 177 178 You may use, modify, and sell products based on these designs, provided you: 179 - Maintain the original copyright notices 180 - Distribute any modified designs under the same license 181 - Make your modifications available in Source format 182 183 ### Software and Firmware 184 The software components—including: 185 - FPGA code (VHDL/Verilog in `/9_Firmware`) 186 - Microcontroller firmware (STM32) 187 - Python GUI and utilities 188 189 remain under the **MIT License** for maximum flexibility. 190 191 ### Full License Texts 192 - The complete CERN-OHL-P license text is in the `LICENSE` file 193 - MIT license terms apply to software where not otherwise specified 194 195 ### Why This Change? 196 Originally, the entire project used the MIT license. The community (special thanks to gmaynez!) pointed out that MIT lacks legal protections needed for physical hardware. The switch to CERN-OHL-P ensures the project is properly protected while maintaining the same permissive spirit. 197 198 ## 📚 Documentation 199 200 Comprehensive documentation is available in the `/docs` folder and served via GitHub Pages at [https://NawfalMotii79.github.io/PLFM_RADAR/docs/](https://NawfalMotii79.github.io/PLFM_RADAR/docs/): 201 202 - [System Architecture](/docs/architecture.html) 203 - [Implementation Log](/docs/implementation-log.html) 204 - [Hardware Bring-Up Guide](/docs/bring-up.html) 205 - [Test Reports](/docs/reports.html) 206 - [Release Notes](/docs/release-notes.html) 207 208 ## 🤝 Contributing 209 210 We welcome contributions! Please see our [Contributing Guidelines](/CONTRIBUTING.md) for details on repo layout, branch workflow, and basic PR checks. 211 212 Areas where help is especially appreciated: 213 - **RF Engineers**: Review designs, optimize antenna performance 214 - **FPGA Developers**: Optimize signal processing pipeline 215 - **Software Developers**: Enhance Python GUI and SDK 216 - **Beta Testers**: University researchers, drone startups, advanced makers 217 218 ## 📞 Contact & Collaboration 219 220 I welcome serious inquiries from researchers, engineers, and potential collaborators. However, due to the high volume of interest in this project, please understand that I cannot guarantee a response to every message. 221 222 - **Technical questions or bug reports**: Please [open a GitHub issue](https://github.com/NawfalMotii79/PLFM_RADAR/issues) so the whole community can benefit from the discussion. 223 - **Collaboration, licensing, or business inquiries**: 📧 nawfal.motii.33 [at] gmail [dot] com 224 225 ## 💰 Sponsors 226 227  228 229 --- 230 231 **Star ⭐ this repository if you're interested in open-source radar technology!** 232 233 *Note: This is an active development project. Some features are still in progress. Check the issues page for known limitations and upcoming features.*